DSO 150 : (Slow) Timebase

Slow Capture

So far, we've captured up to 1ms/division just by selecting the right ADC scaler & rate ( and dropping some samples).

What about slower capture ? i.e. 5mS/div or 100ms/div ?

One option would be to do oversampling i.e. capture much more data at 1ms/div and drop a lot of them

That would require large amount of RAM, for nothing.

The other option is to use a timer.

The scheme is as follows :

* Start a timer and ask for N ADC samples

* When the timer elapses, average the N samples and start a new ADC sampling sequence

* When we have the required number of points, done !

It was a bit tricky to do because there were more timer interrupts than expected (for reason unknown so far).

Triggers

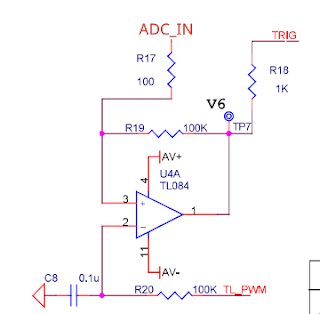

The trigger is based on a OP-Amp comparator, with its output connected to PA8.

The relevant part of the JyeTech schematic is that one :

When input (after scaling) is higher than Vref, PA8 is "One"

When input (after scaling) is lower than Vref, PA8 is "Zero"

So we have to set Vref (taking scaling into account) and the proper interrupt type on PA8 and we have our trigger.

Vref is connected to TL_PWM (PB8) through a low pass RC filter (~ 16 Hz cut-off frequency).

TL_PWM is meant to be used as a PWM, so that the low pass filter will give the duty_cycle *Vcc.

We just need the PWM frequency to be much higher than 16 Hz, not a problem.

Vref=Vcc*DutyCycle

Since it is a 16bits PWM, the max range is 0...65535 noted as 64k

Vref=Vcc*R/64k

The tricky part is that we have to invert the scaling to get the Vref we want i.e.

Pwm DutyCycle = (TriggerVoltage*InputGain+CalibrationZero)*64k/Vcc

CalibrationZero is ~1.5v, we can get a better value from the calibration offset.

Comments

Post a Comment